ムーアの法則は死んでいない、チップレットで生き続ける

半導体業界ではムーアの法則が行き詰まっている、という声はある。しかし、その定義をしっかり見据えると、生き残っているともいえる。米国サンフランシスコで開催されたSEMICON Westではムーアの法則に関するパネルディスカッションが開かれ、意見が分かれた。しかし、ムーアの法則の定義が人によって異なることが、意見の分かれる結果になった。

1965年、Intelを創業する前のFairchild社にいた、Gordon Moore博士はIEEE スペクトラム誌やMcGraw-Hill(マグロウヒル)のElectronics誌に寄稿した論文の中で、シリコンチップの集積化のトレンドを見て「商用化された半導体チップに集積されるトランジスタ数は毎年倍増していく」という経済法則を見出したと述べている。この定義が実は時代と共に変わってきたのである。

例えば、毎年倍増ではなく、18~24カ月ごとに倍増する、と言われるようになった。ただ、このことは、大きなことではない。半導体の基本寸法をデザインルールと呼ぶが、その寸法に限界がやってきたことをムーアの法則の限界と呼ぶ人もいる。このため、ムーアの法則とは別に、デナードの法則(Dennard’s Law)と呼ぶ、微細化が時代と共に進んできたペースもある。これらをロードマップと呼んだりしたこともあった。デナードはIBMワトソン研究所で、MOSトランジスタのスケーリング(比例縮小)法則、すなわち微細化すればするほど、半導体チップは性能が上がり、消費電力が下がるという指針を見出した。

ここにきて微細化技術は行き詰まってきたのであるが、その原因はデザインルールが原子の大きさ(0.5nm程度)に近づいてきたからだ。元々半導体は、n型とp型をドーピングによって作り分けてきた。それもほんのわずかな量でn型とp型をきれいに区別できた。シリコン結晶原子が単位立方cm当たりほぼ10の24乗個あるのに対して、不純物原子をわずか10の15乗個すなわち、10億分の1の量を入れるだけでn型やp型になるのである。だから、半導体トランジスタの誕生後すぐにクリーンルームで製造する必要があった。とはいっても電流として取り出すのは10の18乗以上の単位ではあるが。

Intel社が最初にマイクロプロセッサとメモリを発明した当時は、デザインルールは10ミクロン程度だった。これでも髪の毛の1/5~1/8の太さしかない。今は最先端のプロセスは7nmから5nmへと向かおうとしているが、10nmだとしても当時の1/1000の寸法しかない。実は電流を流す・流さないのしきい値は、不純物濃度に比例するため、原子レベルまで微細になると、例えば10nmの長さの中にシリコン原子は20個くらいしかない。もちろん、1次元の長さではなく3次元の寸法の中を電子が流れるのであるから、10nm×50nm×100nmとするとシリコン原子は20個×100個×1000個=200万個しかない。不純物原子は数えられる程度の数個~十数個しかない。これでは、しきい値のバラツキがとても大きくなり、工業的に制御不能になる。このため不純物濃度に依存しない構造上の工夫によって、しきい値を制御しているのが現状だ。

Gordon Moore氏は、その法則で、シリコンチップ上のトランジスタの集積度はどんどん上がっていくことを表現したのであるが、1個のシリコンチップと定義したため、ムーアの法則は限界にきたと言われるようになった。

しかし、人間が一つのシステムの機能を上げたり、性能を上げたりしようとすると、集積すべきトランジスタ数が増えていくことは実は昔も今も変わっていない。集積すればするほど、システムとしてコストが下がるからだ。この方向はこれからも変わらない。一つの基板上に集積する方がいろいろな基板や巨大な基板に集積するよりも、性能も機能も消費電力もみんな好ましい方向に向かう。

だったら、ムーアの法則の定義を拡張すれば済むのである。半導体企業は、3次元集積や2.5次元集積をできるだけコストを上げずに実現しようとしている。つまり集積するトランジスタ数はもっともっと増えているが、平面上に集積するのではなく、垂直方向の3次元的に集積するのである。3D-ICやNANDフラッシュメモリのように1チップの中に3次元的にメモリ部分だけを重ねていく方向はある。

最近、米国半導体業界で登場してきた、もう一つの方法は、無理やり微細化して詰め込むのではなく、経済的に見合うコストで、例えば28nmや40nmプロセスのように従来技術で経済的に歩留まりが高く可能な限り小さなサイズで集積したチップを作ることである。これらのチップを一つの基板(プラスチックのプリント回路基板でもシリコン自身の基板でもよい)上に集積し配線してつなげていく。1チップに集積するトランジスタ数が数十億個にも達すると製造歩留まりが悪くなる傾向があるからだ。むしろ1個のシリコンチップに無理にトランジスタを詰め込むのではなく、分割して1枚の基板に搭載し無理なく接続する技術を使う。やや大きな基板の上に多数のシリコンチップを載せて接続しても機能を上げ、性能を改善できる。この小さなシリコンチップのことをチップレット(chiplet)と呼ぶ。このチップレット手法が経済的に見合うのであれば、ムーアの法則を乗り越える手法になりうる。

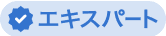

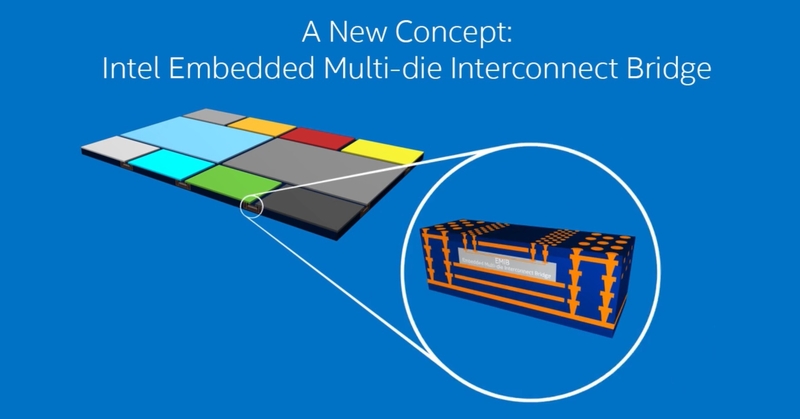

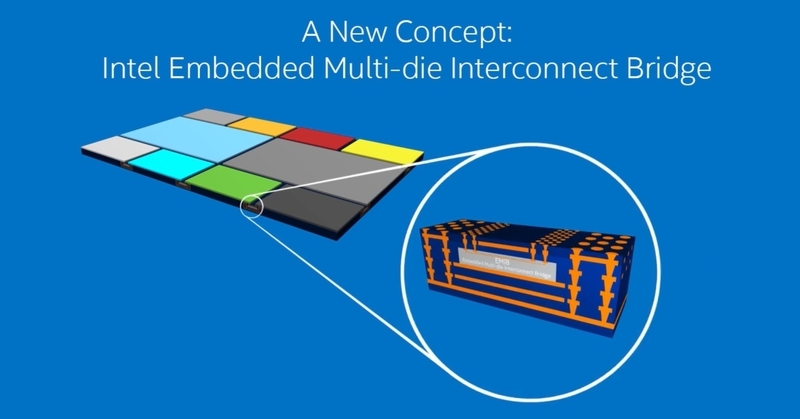

ムーアの法則を長年肯定し続けてきたIntelでさえ、チップレット同士をつなぐ配線実装技術をEMIB(Embedded Multi-die Interconnect Bridge)と呼び、最近注力している。この技術を使えば、HBM2(High Bandwidth Memory)と言われる大容量で高速・広バンド幅のメモリも同一基板上に載せられるため、CPUとのやり取りを短時間ですますことができるようになる。チップ同士の接続部分はチップ程度の大きさのシリコンインターポーザであり、配線は済ませているため、チップ同士の接続にはさほど時間はかからない。これまでは基板全体をシリコンで形成するためコストがかかり、ガラスのインターポーザの提案もあったが、実用化せずに終わりそうだ。

ただ、EMIBでもそう簡単ではないらしい。Intelは今、苦労しながらEMIBを開発しているようだ。

(2019/09/18)