Xilinxの開発者会議で見るムーアの法則3.0

2年ぶりにシリコンバレーにやってきた。今回は、Xilinx(ザイリンクス)の招待で、Xilinx Developer Forum(図1)に出席、取材するためだ。今やシリコンバレーの中心地ともいえるサンノゼのフェアモントホテルで開催、2日間、その場所で会議を楽しんだ。これからのITのメガトレンドに沿ってAIやIoT、5G、デジタルトランスフォーメーション、セキュリティ、クルマなどの設計を見据えた、新しいコンセプトの半導体プラットフォームを提案した。

Xilinxは、プログラムによってハードウエアを自分の好きなデジタル回路に設計できるFPGAという半導体を発明した企業だ。ほぼ同時期にFPGAを開発したAltera(アルテラ)はIntel(インテル)に買収された。XilinxもAlteraも製造工場を持たないファブレスと呼ばれる半導体メーカーだ。

IntelはなぜAlteraを買収したのか。その前からAlteraは製造をIntelに依頼していたという歴史がある。IntelにとってもAlteraからの製造依頼を受けてファウンドリビジネスへと一時広げたが、Alteraを買収することでファウンドリビジネスには興味を失った。その代り、IntelもITのメガトレンドを追い求めはじめ、脱パソコン指向を強めている。パソコンが5年連続マイナス成長を進む中、パソコン用CPUに特化してきたIntelがプラス成長を続けてきたのは、ITのメガトレンドを追求してきたからだ。

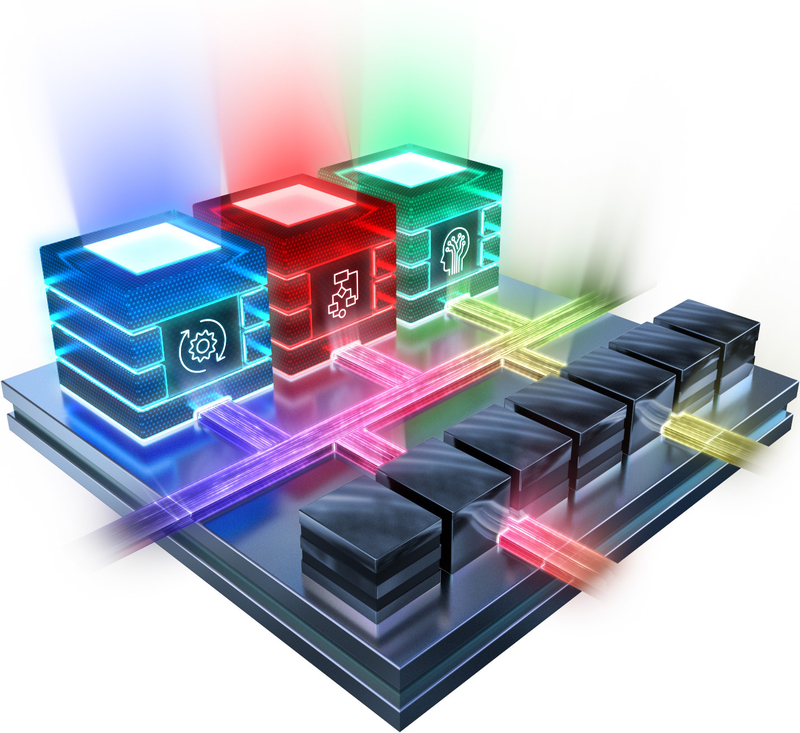

ITのメガトレンドを追求するのはXilinxも同じ。IntelがCPUやGPUなどからFPGAを取り込む2.5Dのプラットフォームソリューションを提案しているに対して、XilinxはFPGAからCPUやGPUを取り込む方向で、行きつくところは似たものになった。XilinxがACAP(Adaptive Compute Acceleration Platform)と呼ぶ新しい半導体プラットフォームもやはり2.5Dのソリューションである。このプラットフォームは、いわば2.5次元半導体集積回路というべきもので、実はXilinxは、ムーアの法則を突破するこの2.5D-ICを5年くらい前から開発してきた。このためこのACAPの実現はそう遠い話ではない。今年の末か来年初めには市場に出てくる。

今回は、さらにAI専用チップや高精度のDSPチップ、さらにArmの最高級CPUコアであるCortex-A72などを集積したSoC、そしてXilinxがダイナミックに再構成可能な(リコンフィギュアラブル)FPGA回路を敷き詰めたVERSALチップ、さらに周辺回路や3次元メモリICであるHBM2、SerDes(シリアル→パラレル変換+パラレル→シリアル変換)などの各チップを交通整理するNoC(Network on Chip)というスイッチング配線技術で結ぶという、超高級半導体の詳細を発表した。

この最高級2.5D集積回路は、シリコンインターポーザ(各チップの接続パッドを多層配線で結ぶためだけのシリコン)を介して構成される。まさに設計・プロセス・実装が一体となったプラットフォーム半導体ソリューションである。例えばAIの推論を重視するチップを集積したい場合は、ディープラーニング用のチップを集積し、高精度なDSPを軽くする、しかもアルゴリズムをダイナミックに切り替えたいという応用には、VERSAL(図2)を用意する。さまざまな応用に使える、最高級ながら汎用のプラットフォームとする。VERSALは、多様性という意味のVersatileと、汎用という意味のUniversalを組み合わせた造語である。

ムーアの法則が行き詰まり、もはや半導体ビジネスは終わった、と考える人は米国にはもういなくなっている。AIもIoTも5Gもセキュリティもクラウドも自動運転車や事故を起こさないクルマも全て半導体が制御して実現するからである。

ただ、ムーアの法則が行き詰っていることは事実である。ムーアの法則は、「市販のシリコンチップ上に集積されるトランジスタの数は毎年2倍のスピードで増えていく」、という定義の経済法則だった。年率2倍が、18~24カ月に2倍というスピードに変わったが、これもムーアの法則と呼んできた。半導体集積回路は最小寸法10ミクロンくらいから出発し、今やその1/1000以下の7nm、次は5nmへと微細化が進んできた。しかし、nm単位になると原子の大きさに近付いてくる。もともと半導体トランジスタは、何千・何万個の電子を制御するものだったが、その数が数十個から数個になってくると、1個1個のトランジスタの特性がばらつくことになり、もはや集積回路で制御できなくなってきている。だからムーアの法則は限界といわれる。

ところが、半導体ICを使う人たちにとって、さまざまな機能を半導体に集積し、性能を上げ消費電力を下げてきたICを求める姿勢は変わらない。さらに集積度を上げてくれという要求は全く変わっていない。だから、ムーアの法則を再定義する必要がある。最初のムーアの法則をムーアの法則1.0とするなら、More than MooreやMore Mooreと言われた時代をムーアの法則2.0とする。そして、かつて東芝の専務取締役で半導体開発の先頭に立っていた香山晋氏は、最近の状況をムーアの法則3.0という言葉で表現する。

ムーアの法則3.0を1パッケージ内に集積されるトランジスタの数は、数年に2倍で増加すると定義し直せば、ムーアの法則3.0はこの先も続くことになる。