Intel Foundryが「半導体製造のブレイクスルー」をIEDM 2024で披露 AI半導体の進化に貢献

Intelは12月7日(米国太平洋時間)、IEEE International Electron Devices Meeting(IEDM)の第70回会合において、同社の半導体受託生産(ファウンドリー)事業「Intel Foundry」向けに進めてきた半導体生産の最新技術に関する論文を公開した。同社は論文に記載した最新技術を「将来のAI需要にかなう、業界初の進化」だとしている。 【画像】論文掲載内容の一部

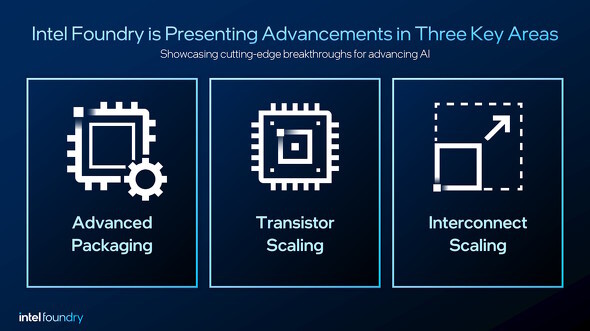

最新技術の概要

Intel Foundryでは、将来的なAIの進歩を見越して「先進的なパッケージング」「トランジスタのスケーリング」「インターコネクト(半導体間の電気的接続)」の3分野に注力して研究を推進している。それは「ムーアの法則」の継続にも必要なことだという。 今回の発表した論文も、この3分野に関連するもので、将来的に銅トランジスタで予想される“制約”を克服することや、アセンブリ技術を改善すべく進められたものだという。 先進的なパッケージング パッケージング面では、1μm未満の厚さのチップレットでも高速にアセンブリできる「選択的レイヤー転送」の開発に取り組んだ。現行のHI(異種チップ集積技術)における技術的課題を解決すべく、無機赤外線レーザーを使った剥離を実証したという。 加えて、容量/帯域幅/遅延のボトルネックを解決するための高度なメモリの統合技術、異種コンポーネント間の電力効率と帯域幅密度を高めるためのハイブリッドボンディング、遅延と帯域幅に関する制限を避けるためのモジュール式システム拡張にも取り組んだとのことだ。 トランジスタのスケーリング トランジスタのスケーリングという面では、Intelの独自技術である「RibbonFET」のを限界まで適用することにチャレンジし、ゲート長6nmのシリコンRiboonFET CMOSトランジスタの製作に成功したという。このことは、先述した「『ムーアの法則』の継続」という観点で大きな意味を持つ。 加えて、ゲート長を30nmまで短くしたGAA構造の二次元NMOS/PMOSトランジスタの製造に関する取り組みも披露している。これは将来的にウエハの主要原料であるシリコンの代替として、TMD(二次元遷移金属ダイカルコゲナイド)を使った半導体の生産につなげる狙いもあるようだ。 インターコネクト 異なる半導体回路をつなぎ合わせるインターコネクトという観点では、現実的なコスト効率を備え、大量生産にかなう減算型ルテニウム層を使ったインターコネクトについて披露する。25nm未満のピッチの整合抵抗環境下で静電容量を最大25%確保できたという。 本技術はまだ「研究開発」の段階にある技術だが、将来の半導体ノードで使われる可能性があるという。

ITmedia PC USER