EUVリソグラフィ向けフォトマスク上に2nm世代以降の微細なパターンの解像に成功

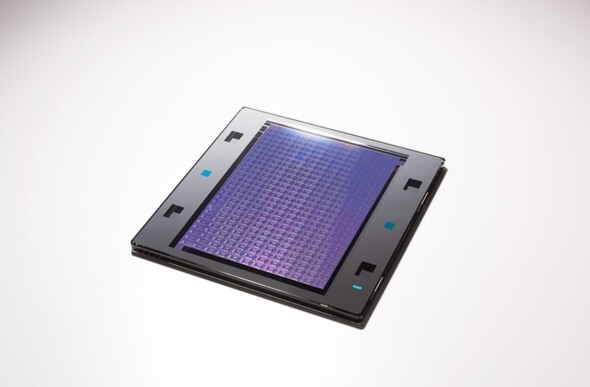

大日本印刷(DNP)は2024年12月12日、半導体製造の最先端プロセスであるEUV(Extreme Ultra-Violet:極端紫外線)リソグラフィに対応した、2nm世代以降のロジック半導体向けフォトマスクに要求される微細なパターンの解像に成功したと発表した。 EUVリソグラフィ用フォトマスク上の線幅17nmのライン&スペースのパターン画像[クリックで拡大] 出所:DNP また、DNPは、2nm世代以降の次世代半導体向けに適用が検討されている高開口数(High-Numerical Aperture、高NA)に対応したフォトマスクの基礎評価が完了し、半導体開発コンソーシアムや製造装置メーカー、材料メーカーなどへ評価用フォトマスクの提供を開始した。高NA-EUVリソグラフィは、従来に比べて高い解像度の微細なパターンをシリコンウエハー上に形成することを可能にしている。これにより高性能かつ低消費電力の半導体の実現が期待されている。

開発のポイント

2nm世代以降のEUVリソグラフィ向けフォトマスクの実現には3nm世代に比べて、20%以上縮小されたパターンが要求される。サイズだけでなく形状も一般的な直線や矩形(くけい)のパターンだけでなく、複雑さを増した曲線パターンを含めた、全ての微細なパターンを同一マスク上で解像させる技術が必要となる。DNPは確立済みの3nm世代の製造プロセスをベースに改善を重ねることで、2nm世代以降に要求されるパターンの解像を達成した。 高NA-EUVリソグラフィ用のフォトマスクについては、通常のEUVリソグラフィ用に比べ、より高い精度と微細な加工が要求される。DNPは通常のEUVリソグラフィ向けフォトマスクとは異なる製造プロセスフローを構築した上で最適化を行った。 今後DNPは、製造の歩留まり向上などの生産技術の確立を進め、2027年度の2nm世代ロジック半導体向け量産フォトマスクの供給開始を目指す。引き続きベルギーに本部を置く国際研究機関であるimecとも協力し、1nm世代も見据えたフォトマスク製造技術の開発を推進する。

開発の背景

近年、最先端のロジック半導体ではEUV光源を用いるEUVリソグラフィによる量産が進み、メモリ半導体でもその採用が拡大するなど、最先端半導体の供給にEUVリソグラフィが必要となっている。 DNPは2023年に、3nm世代のEUVリソグラフィ向けフォトマスク製造プロセスの開発を完了した。2024年には、Rapidusが参画している新エネルギー・産業技術総合開発機構(NEDO)の「ポスト5G情報通信システム基盤強化研究開発事業」に再委託先として参画し、最先端ロジック半導体向けフォトマスク製造プロセスおよび保証に関わる技術を開発している。

MONOist