IBMとRapidusが2nmプロセス半導体の量産に向け「重要なマイルストーンに到達」

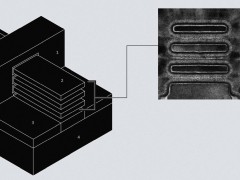

IBMの研究部門であるIBM ResearchとRapidusは2024年12月10日(現地時間)、新たなエッチングプロセスであるSLR(Selective Layer Reductions:選択的薄膜化)を用いて、マルチ閾値電圧を持つナノシートGAA(Gate All Around)トランジスタを製造できるようになったと発表した。ナノシートGAAトランジスタによって実現される2nmプロセス半導体の量産に向けて「重要なマイルストーンに到達した」(IBM Research)とする。 【ナノシートGAAトランジスタの構造】 IBMの2nmプロセス半導体では、積層された3枚のナノシートをゲートで取り囲んだ構造を持つナノシートGAAトランジスタが特徴となっている。3nmプロセス以前の半導体で採用されてきたFinFETトランジスタと比べたときの課題として挙げられているのが、FinFETより構造が複雑なナノシートGAAトランジスタにおいて、低消費電力が重視される場合に必要な高い閾値電圧とAI(人工知能)半導体など高性能コンピューティング向けの低い閾値電圧の両方を可能にするマルチ閾値電圧のプロセス技術の確立だった。 IBMは2017年にナノシートGAAトランジスタを発表してから、マルチ閾値電圧の確立に向けた課題を順次解決してきたとする。今回発表したのは、集積度の高い2nmナノシートGAAトランジスタで極めて狭くなるN-P境界(n型とp型の半導体チャネル間の距離)において、高い閾値電圧に必要な薄膜の加工と低い閾値電圧に必要な厚膜の加工を可能にする2つのSLRである。 2nmプロセス半導体では、N-P境界が40nm未満の距離になることがあり、薄膜を作り込む際にゲートの境界部分のアンダーカット(エッチングが横方向に進行する現象)に対応するマージンが少なくなり構造上の問題が発生する可能性がある。そこで、新たなエッチングプロセスである「SLR1」を開発し、2つのトランジスタ間の極小スペースであるN-P境界においてアンダーカットの問題に対処した。 また、厚膜の加工で発生する類似のアンダーカットの問題に対処する「SLR2」も開発した。実験では、トランジスタのゲートに影響を与えることなくアンダーカットを回避しながら、N-P境界でのみ材料を薄くできることを実証したという。 今回発表したマルチ閾値電圧の技術はRapidusに移管され、北海道千歳市に建設中の工場「IIM-1」での2nmプロセス半導体の量産に適用される計画だ。 なお、今回の研究成果は、米国サンフランシスコで開催されている半導体/電子デバイスの国際会議「第70回 IEDM(International Electron Devices Meeting) 2024」(同月7~11日)において、IBM ResearchとRapidusの共著の研究論文として発表された。

MONOist